MIPS Architecture 32-bit processor written in VHDL for Fundementals/Computer Design

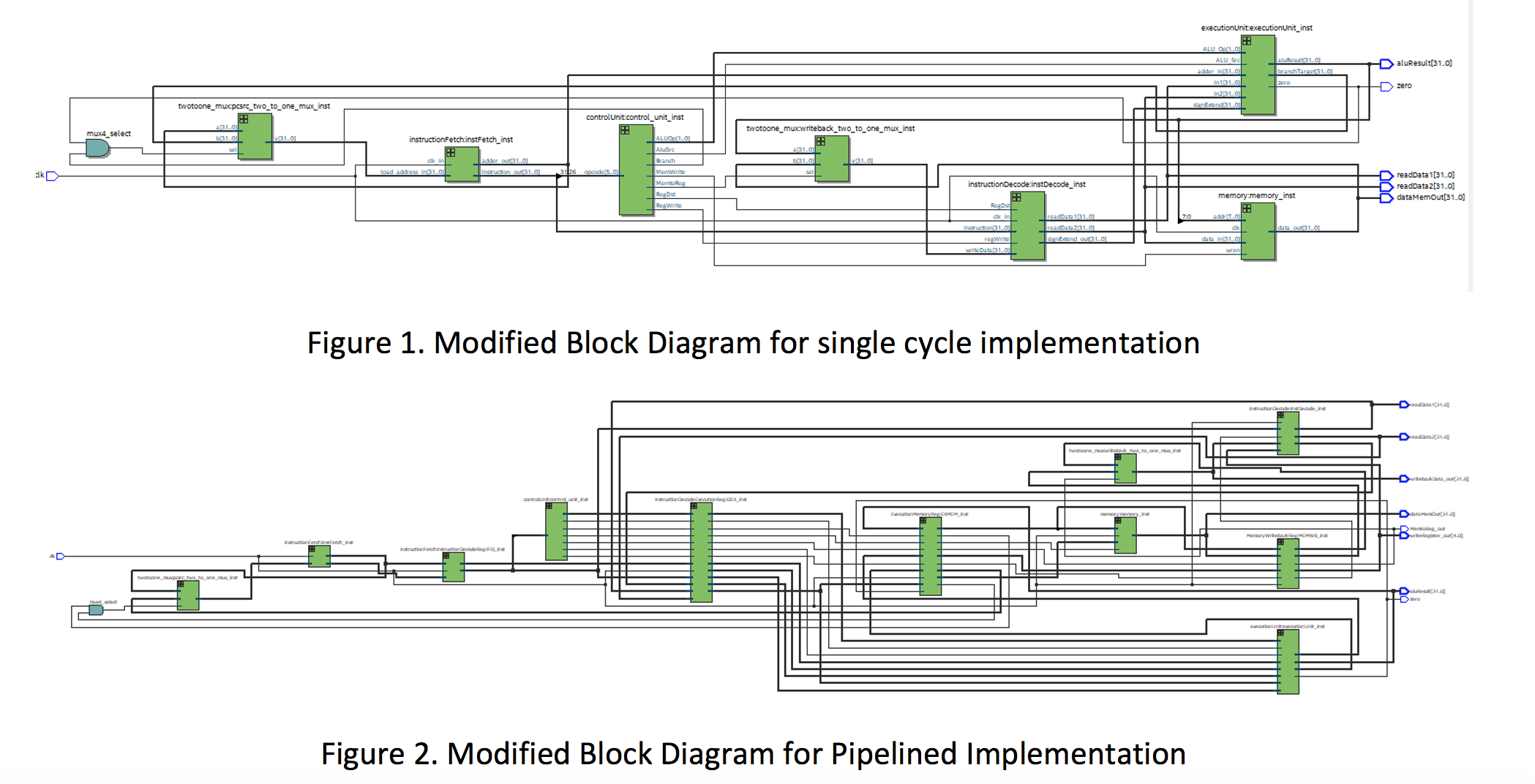

This project was conducted in three phases over the course of the semester and was created to facilitate learning computer central processing unit design. The processor designed had five basic stages: instruction fetch, instruction memory, instruction execute, data memory, and write-back. A single cycle and pipelined version were created. The project was also pushed to the DE-10 Lite FPGA in its pipelined implementation and worked as designed, computing the MIPS instructions: branch, branch equal/ not equal, immediate instructions, add and subtract, store and load word, and all logical expressions (or, and, xor, etc.).

Waveforms were generated and analyzed for correctness in ModelSim. More detail can be provided for this project on request. Final project presentation available here.

| Image: MIPS Architecture |

|---|

|