## Successful implementation of single cycle and pipelined MIPS architecture design

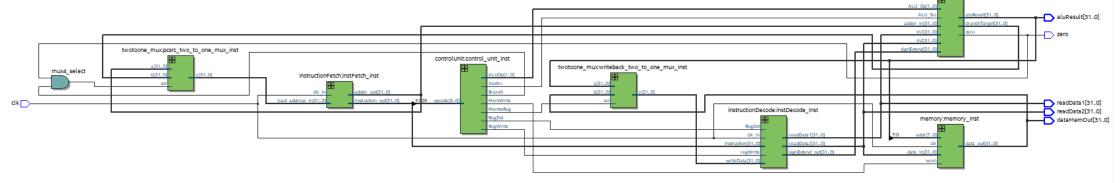

Single cycle implementation

executionUnit:executionUnit\_inst

### **Register/ Memory Loading**

- Registers were loaded in the the instruction memory with addi instructions

- addi \$t1, \$zero, 0x112

- addi \$t2, \$zero, 0xA

- addi \$t3, \$zero, 0xF

- Memory loading was done using memory initialization files (.mif) files

```

CONTENT BEGIN

0010000000010010000000100010010;--load phase addi $11, $zero, 0x112, so that $11 = 0x112

00

001000000000101000000000000000001010;--load phase addi $t2, $zero, 0xA, so that $t2 = 0xA

02

0010000000010110000000000001111;--load phase addi $t3, $zero, 0xF, so that $t3 = 0xF

00010001001010100000000000000011; -- beg $t1, $t2, Equal

03

00000001001010100100100000100000; -- add $t1, $t1, $t2

10101101010010110000000001100100; -- sw $t3, 100($t2)

05

00000001001010100100100000100101;--or $t1, $t1, $t2

06

08

0B

0C

CONTENT BEGIN

0010000000010010000000100010010;--load phase addi $11, $zero, 0x112, so that $11 = 0x112

0010000000010110000000000001111;--load phase addi $t3, $zero, 0xF, so that $t3 = 0xF

00000000000000000000000000000000;--stall

000000000000000000000000000000000000:--stall

000000000000000000000000000000000000;--stall

00010001001010100000000000000011; -- beg $t1, $t2, Equal

00000001001010100100100000100000; -- add $t1, $t1, $t2 (result 0x11C)

10101101010010110000000001100100;--sw $t3, 100($t2)

09

00000001001010100100100000100101;--or $t1, $t1, $t2 (result 0x11A)

00000000000000000000000000000000000;--equal

Nathan Gardner

```

#### Data memory implantation Memory initialization file

```

CONTENT BEGIN

0000000000000000000000000000

```

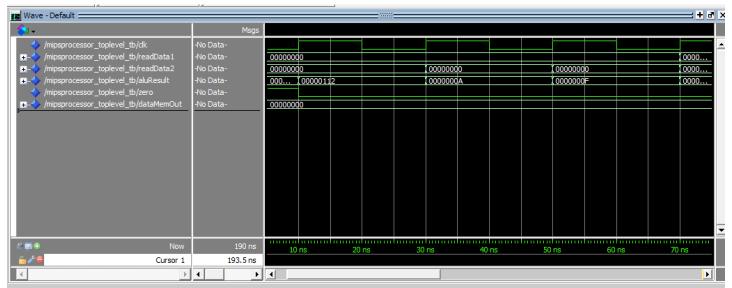

# Single cycle successful implementation

### Register load phase

### **Program Execution Phase**

beq: 0x112 - 0xA = 0x108 != 0(branch not taken)  $\checkmark$

add:  $0x112 + 0xA = 0x11C \checkmark$

sw: dataMemOut updated next cycle, because \$t3 = 0xF

or:  $0x11C OR 0xA = 0x11E \checkmark$

## Single cycle successful implementation (beq taken)

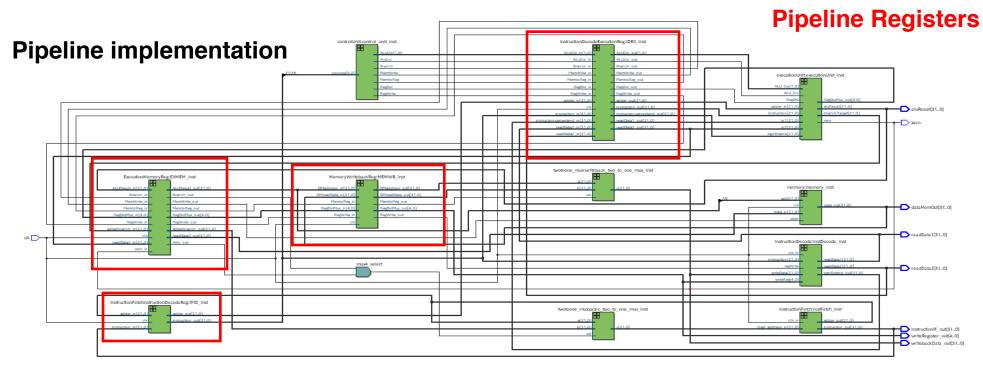

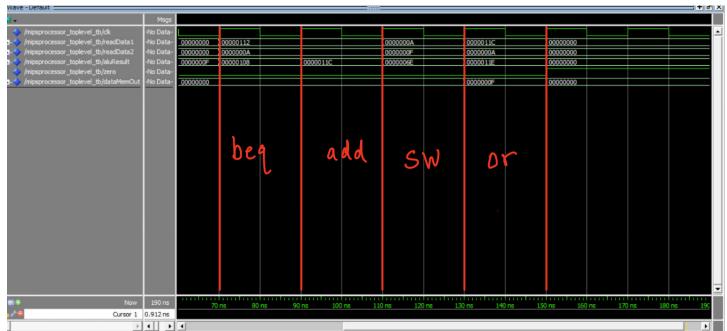

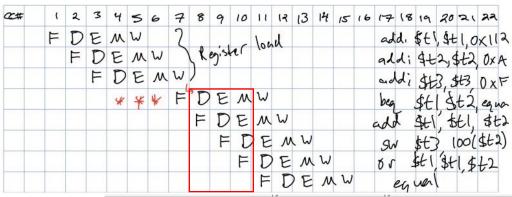

### Pipeline successful implementation

Show successful implementation of pipeline with clock cycles 8,9, and 10.